### VANYA YANEVA

vanya.yaneva@ed.ac.uk

- PhD Candidate in Software Testing at the University of Edinburgh.

- My background is in High Performance Computing.

- My PhD work is on accelerating software testing by executing tests in parallel on the GPU.

- I am interested in:

- functional software testing

- parallel architectures and programming models

- compiler optimisations and compiler-based tools

# ACCELERATED FINITE STATE MACHINE TEST EXECUTION USING GPUS

#### Vanya Yaneva Arnav Kapoor, Ajitha Rajan, Christophe Dubach

Published in APSEC'18

HYDERABAD

EPSRC Centre for Doctoral Training in Pervasive Parallelism

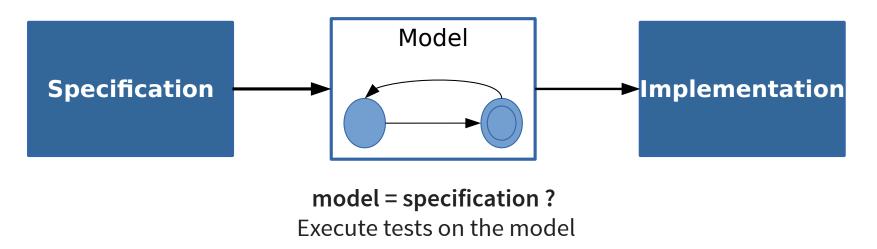

### **MODEL-BASED DEVELOPMENT**

Software is *implemented* and *tested* based on a model.

There are many ways to define a model:

• UML • formal specification languages (Z, B, Alloy) • block/state charts

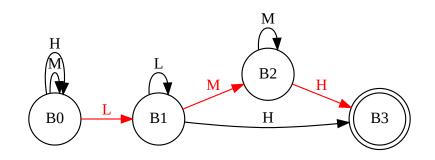

## FINITE STATE MACHINES (FSMS)

#### A common model for a variety of systems.

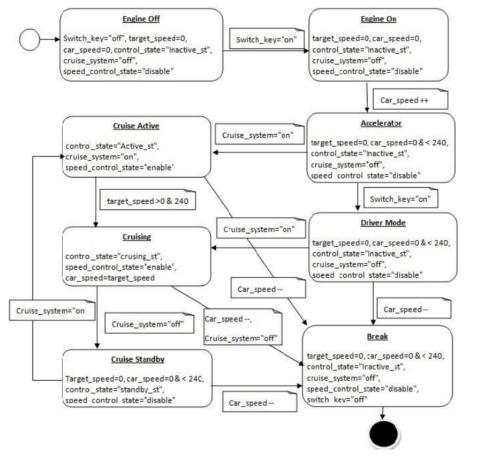

control systems [Saifan&Mustafa 2014]

#### network intrusion detection <sup>[Xu et al. 2014]</sup>

signal processing tools [Lehane et al. 2016]

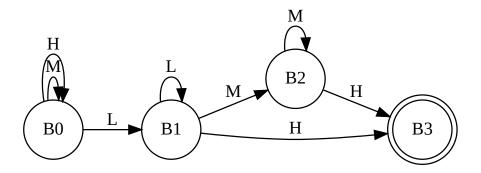

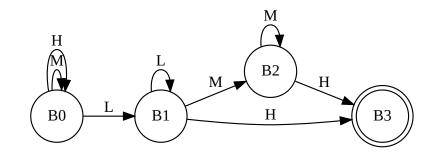

#### FINITE STATE MACHINES (FSMS)

Model for a digital oscilloscope **KEYSIGHT**

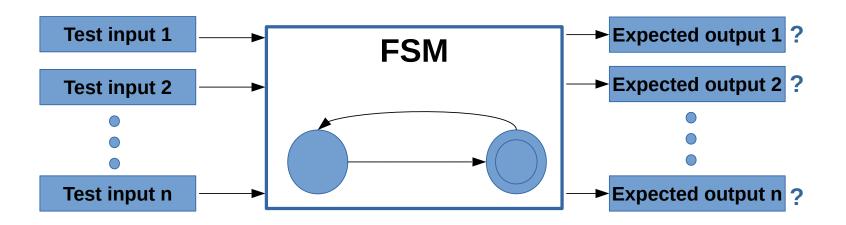

#### **TESTING FSMS**

Functional (black-box) testing

1. Generate the test inputs

- 2. Execute the tests

- 3. Check the results

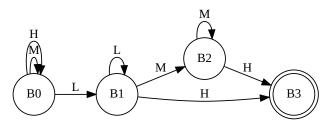

### **GENERATING TESTS**

based on coverage criteria

All-state coverage:

• MLMH -> 0001

**X** weak fault-finding <sup>[Briand et al. 2004]</sup>

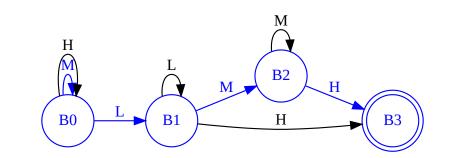

#### **GENERATING TESTS**

based on coverage criteria

All-transition coverage:

- HLLMMH -> 000001

- MLH -> 001

**×** weak fault-finding [Briand et al. 2004]

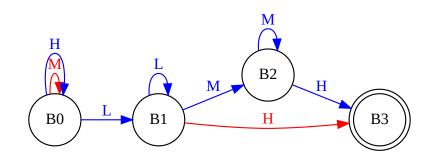

### **GENERATING TESTS**

based on coverage criteria

All-transition pair coverage:

- HLLMMH -> 000001

- MLH -> 001

- LMH -> 001

✓ strong fault-finding <sup>[Briand et al. 2004]</sup>

### THE PROBLEM

Some finite state machines:

states and transitions

test sequences

hours to execute

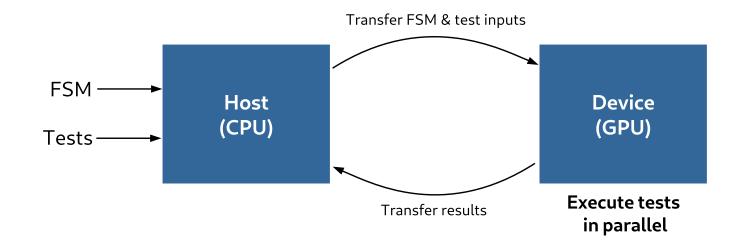

### **OUR APPROACH**

Execute the tests in parallel on the GPU.

• Cheap and widely available • Provide thousands of thread

one GPU thread = one test

#### WE HAVE DONE IT BEFORE

#### for testing **embedded** C programs.

#### **Compiler-Assisted Test Acceleration on GPUs** for Embedded Software Aiitha Raian

Vanva Yaneva School of Informatics University of Edinburgh, UK vanya.vaneva@ed.ac.uk

ABSTRACT

sensors. Embe produce safe critical to alle requires using increasing tin Speeding u tance for emb by running, i

puters. Howe maintenance

developers ha

Units) for rur

available in m

lelism makin

In this paper

tions of embe

resource. We propos

Christophe Dubach School of Informatics School of Informatics University of Edinburgh, UK University of Edinburgh, UK arajan@staffmail.ed.ac.uk christophe.dubach@ed.ac.uk

ACM Reference format: Vanya Yaneva, Ajitha Rajan, and Christophe Dubach. 2017. Compiler-Assisted Embedded software is found everywhere from our highly visible Test Acceleration on GPUs for Embedded Software. In Proceedings of 26th mobile devices to the confines of our car in the form of smart um on Software Testing and Analysis Santa Barbar

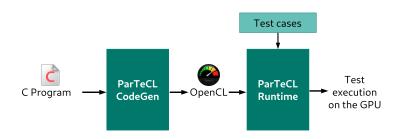

#### ParTeCL: Parallel Testing using OpenCL\*

following goals,

test execution.

the program.

os the nonform

tential to execute a large number of test cases concurrently.

However, GPUs are notoriously hard to program and require

significant expertise and a thorough understanding of the

hardware and programming model to unlock their potential

execution using our ParTeCL framework. ParTeCL has the

We plan to address these problems in the context of test

(1) Increase the usability and feasibility of GPUs for

(2) Increase the performance and effectiveness with

Our recently accepted paper [10] in the main research track

of ISSTA 2017 presents empirical evaluations of our approach

compiler optimisations that analyse the tests and

man and offectiv

| Vanya Yaneva                                                                                                                                                                                                                                                                                                    | Ajitha                                                               | Rajan                                                                                                           | Christophe Dubach                                                                                                                                                                                                                                                                                                       |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| University of Edinburgh, UK<br>vanya.yaneva@ed.ac.uk                                                                                                                                                                                                                                                            | University of H<br>arajan@staff                                      |                                                                                                                 | University of Edinburgh, UK<br>christophe.dubach@ed.ac.uk                                                                                                                                                                                                                                                               |  |

| ABSTRACT<br>With the growing complexity of software, the<br>cases needed for effective validation is extrem<br>cuting these large test suites is expensive and t<br>putting an enormous pressure on the softwar<br>cycle. In previous work, we proposed using<br>cessing Units (GPUs) to accelerate test execut | ely large. Exe-<br>ime consuming,<br>ce development<br>Graphics Pro- | suite. This approach<br>infrastructure, main<br>day commodity par<br>cessing Units (GPU:<br>also being cheap, e | to reduce execution time of the entire test<br>h, however, is costly in terms of resources,<br>ntenance and energy consumed. Present<br>rallel accelerators, such as Graphics Pro-<br>s), offer enormous computing power while<br>easily available and energy efficient. A<br>housands of parallel threads with the po- |  |

a GPU, without approach wh kernels for pa cessing Units (GPUs) to accelerate test execution by running test cases in parallel on the GPU threads. However, the complexity of GPU programming poses challenges to the nique, we acl CPU executio usability and effectiveness of the proposed approach. In this paper we present ParTeCL - a compiler-assisted standard emb

framework to automatically generate GPU code from sequen CCS CON tial programs and execute their tests in parallel on the GPU We show feasibility and performance achieved when execut- Software a ing test suites for 9 programs from an industry standard bugging: Sou benchmark suite on the GPU. ParTeCL achieves an average nization  $\rightarrow$ speedup of 16× when compared to a single CPU for these benchmarks KEYWOR CCS CONCEPTS

Functional te Software and its engineering →Software testing and debugmated testing ging; Source code generation; •Computer systems organiza-

ISSTA'17

Max. speedup 53x (avg. 16x)

- on 9 subjects from **EEMBC** embedded benchmark suite

- when compared to a single CPU

- Completely automated parallel testing on the GPU

In our current work we *extend* ParTeCL Runtime, providing a **completely automated** process.

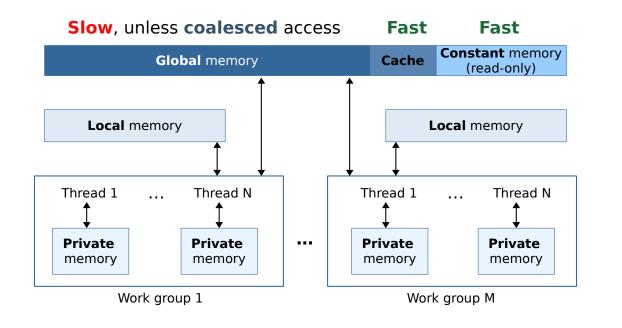

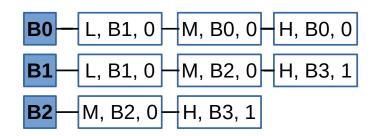

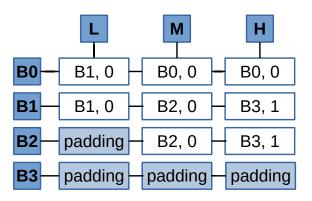

### **FSMS ARE DIFFERENT TO C PROGRAMS**

FSM execution involves *a lot* of memory accesses.

- FSM and tests are in *global* memory.

- **FSM** is in *constant* memory (if it fits).

To improve performance we need:

compact representation AND/OR coalesced access

We investigate **2 FSM** memory layouts and **3 test** memory layouts.

### **RESEARCH QUESTIONS**

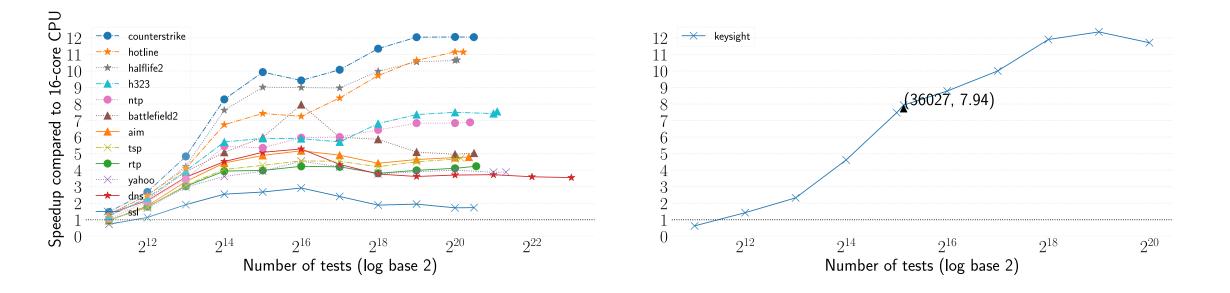

- RQ1: Test execution speedup What is the speedup on the GPU, compared to a 16-core CPU?

- RQ2: FSM layout

Does the choice of FSM layout influence the speedup?

• RQ3: Test layout

Does the choice of test layout influence the speedup?

• RQ4: Sorting the tests based on length Does sorting the tests influence the speedup?

#### **EXPERIMENT SUBJECTS**

| FSM                  | Domain                          | #States | #Inputs | #Tests    |

|----------------------|---------------------------------|---------|---------|-----------|

| ssl                  | intrusion detection (17-filter) | 34      | 256     | 1 475 251 |

| battlefield2         | intrusion detection (17-filter) | 71      | 256     | 1 476 796 |

| dns                  | intrusion detection (17-filter) | 197     | 256     | 8 533 671 |

| aim                  | intrusion detection (17-filter) | 41      | 256     | 1 344 963 |

| rtp                  | intrusion detection (17-filter) | 28      | 256     | 1 536 723 |

| tsp                  | intrusion detection (17-filter) | 27      | 256     | 1 162 511 |

| yahoo                | intrusion detection (17-filter) | 54      | 256     | 2 627 405 |

| ntp                  | intrusion detection (17-filter) | 31      | 256     | 1 374 296 |

| hotline              | intrusion detection (17-filter) | 34      | 256     | 1 216 433 |

| h323                 | intrusion detection (17-filter) | 46      | 256     | 2 241 832 |

| halflife2            | intrusion detection (17-filter) | 24      | 256     | 1 088 409 |

| counterstrike-source | intrusion detection (17-filter) | 30      | 256     | 1 472 463 |

| keysight             | digital signal processing       | 4004    | 3       | 36 027    |

Tests generated based on *all-transition pair* criteria.

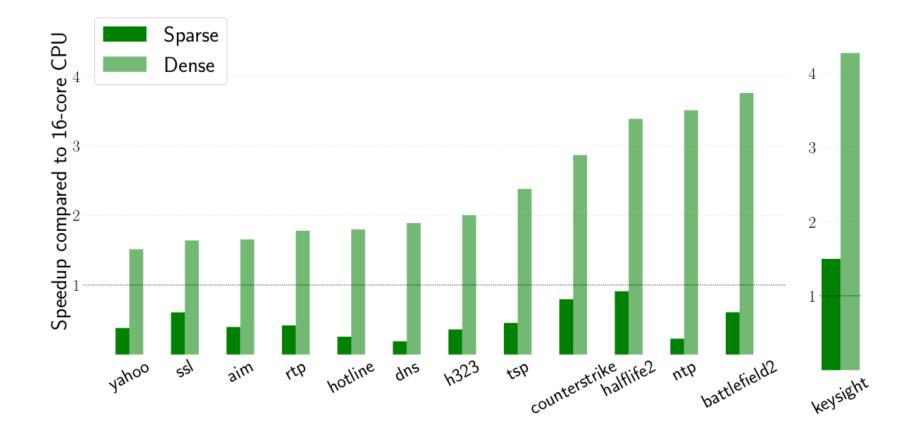

#### **RQ1: TEST EXECUTION SPEEDUP**

using the fastest configurations for GPU and 16-core CPU

Max. speedup 12x (avg. 6.4x)

#### **RQ2: FSM LAYOUT IN MEMORY**

#### Sparse

- < compact encoding

- **X** expensive search for each test input

#### Dense

- constant search for each test input

- X padding adds memory overhead

#### **RQ2: FSM LAYOUT IN MEMORY - RESULTS**

Max. speedup 4.2x

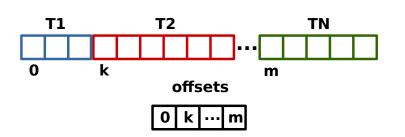

#### **RQ3: TEST LAYOUT IN MEMORY**

#### Padded

- < easy to implement

- X padding adds memory overhead

- X no memory coalescing

#### Padded-transposed

•

memory coalescing

#### With-offsets

- X no memory coalescing

- < compact layout

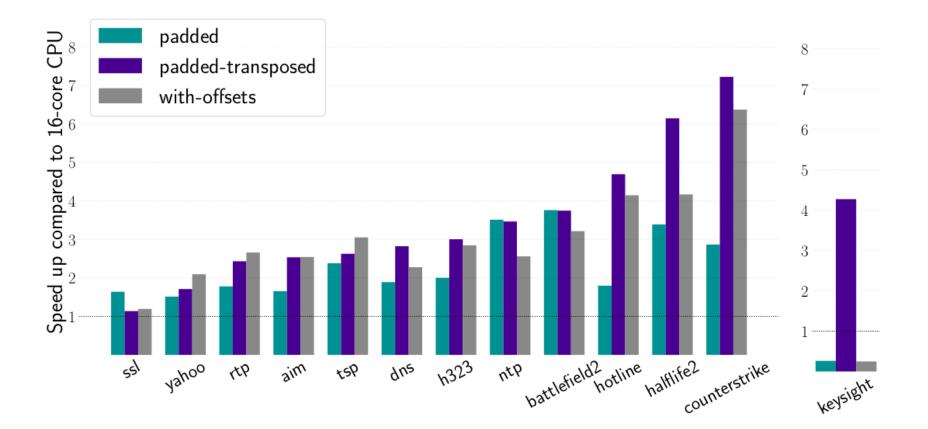

#### **RQ3: TEST LAYOUT IN MEMORY - RESULTS**

Max. speedup 7.8x

### **RQ4: SORTING TESTS BASED ON LENGTH - RESULTS**

Max. speedup 12x (avg. 6x)

## SUMMARY

GPUs can accelerate functional testing of FSMs.

Speedup compared to 16-core CPU is **max. 12x** (avg. 6x) with optimised FSM/test layout and load balancing.

We have automated the process.

github.com/wyaneva/partecl-runtime

### REFERENCES

- 1. [Saifan&Mustafa 2014] Using Formal Methods for Test Case Generation According to Transition-Based Coverage Criteria - Scientific Figure on ResearchGate. Available from: https://www.researchgate.net/figure/Cruise-controlsystem-finite-state-machine-diagram\_fig2\_283902282 [accessed 4 Dec, 2018]

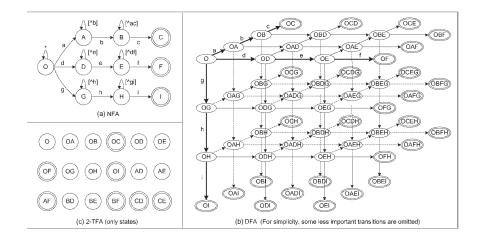

- 2. [Xu et al.2014] Xu, Yang et al. TFA: A Tunable Finite Automaton for Pattern Matching in Network Intrusion Detection Systems. IEEE Journal on Selected Areas in Communications 32 (2014): 1810-1821.

- 3. [Lehane et al. 2016] Lehane et al. Digital Triggering Using Finite State Machines. US Patent App. 14/957,491. March 2016

- 4. [Briand et al. 2004] Briand et al. Using Simulation to Empirically investigate Test Coverage Criteria Based on Statechart. *In ICSE 2004*